Product Summary

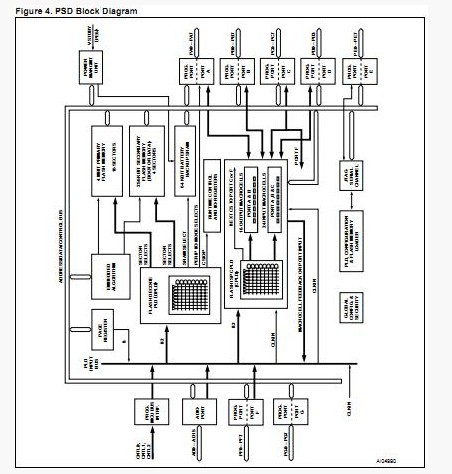

The PSD4235G2-90UI is a memory system for microcontrollers (MCUs) brings In-System-Programmability (ISP) to Flash memory and programmable logic. The result is a simple and flexible solution for embedded designs. The PSD4235G2-90UI combines many of the peripheral functions found in MCU based applications. It integrates an optimized Macrocell logic architecture. The Macrocell was created to address the unique requirements of embedded system designs. The PSD4235G2-90UI allows direct connection between the system address/data bus, and the internal PSD registers, to simplify communication between the MCU and other supporting devices.

Parametrics

PSD4235G2-90UI absolute maximum ratings: (1)TSTG, Storage Temperature: –65 to 125℃; (2)TLEAD, Lead Temperature during Soldering (20 seconds max.): 235℃; (3)VIO, Input and Output Voltage (Q = VOH or Hi-Z): –0.6 to 7.0 V; (4)VCC, Supply Voltage: –0.6 to 7.0 V; (5)VPP, Device Programmer Supply Voltage: –0.6 to 14.0 V; (6)VESD, Electrostatic Discharge Voltage (Human Body model): –2000 to 2000 V.

Features

PSD4235G2-90UI features: (1)dual bank flash memories: 4 Mbit of Primary Flash Memory (8 uniform sectors, 32K x 16); 256 Kbit Secondary Flash Memory with 4 sectors; Concurrent operation: read from one memory while erasing and writing the other; (2)64 Kbit SRAM (battery backed); (3)PLD with macrocells: Over 3000 Gates of PLD: CPLD and DPLD; CPLD with 16 Output Macrocells (OMCs) and 24 Input Macrocells (IMCs); DPLD - user defined internal chip select decoding; (4)seven L/O ports with 52 I/O pins: 52 individually configurable I/O port pins that can be used for the following functions: MCU I/Os; PLD I/Os; Latched MCU address output; Special function l/Os; l/O ports may be configured as open-drain outputs; (5)in-system programming (ISP) with JTAG: Built-in JTAG compliant serial port allows full-chip In-System Programmability; Efficient manufacturing allow easy product testing and programming; Use low cost FlashLINK cable with PC; (6)page register: Internal page register that can be used to expand the microcontroller address space by a factor of 256; (7)programmable power management; (8)high endurance: 100,000 Erase/write Cycles of Flash Memory; 1,000 Erase/WRITE Cycles of PLD; 15 Year Data Retention; (9)single supply voltage: 5V ±10%; (10)memory speed: 70ns Flash memory and SRAM access time.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

PSD4235G2-90UI |

STMicroelectronics |

CPLD - Complex Programmable Logic Devices 5.0V 4M 90ns |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

PSD4000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PSD4135G1V-70J |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PSD4135G2 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PSD4135G2-90U |

STMicroelectronics |

SPLD - Simple Programmable Logic Devices U 511-PSD4235G2-90U |

Data Sheet |

Negotiable |

|

||||

|

PSD4135G2V-90U |

STMicroelectronics |

SPLD - Simple Programmable Logic Devices TQFP-80 3V 1M 90N |

Data Sheet |

Negotiable |

|

||||

|

PSD4235G1V-90J |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))